# User's Guide

Publication Number E2467-97002 January 1997

For Safety Information, Warranties, and Regulatory Information, see the pages at the end of this manual.

© Copyright Hewlett-Packard Company 1997 All Rights Reserved.

# HP E2467A Intel APIC Bus Preprocessor Interface

## The HP E2467A Preprocessor Interface—At a Glance

The HP E2467A Preprocessor Interface provides an APIC Bus interface for state analysis between any Intel APIC Bus target system and an HP logic analyzer. The HP E2467A can be used with the HP E2457A Preprocessor Interface to provide state, timing, and APIC analysis of an Intel Pentium® target system, or it can be used with the HP E2466A/B Preprocessor Interface to provide state, timing, and APIC analysis of an Intel Pentium® Pro target system. The following logic analyzers are supported for the listed configurations.

#### Logic Analyzers Supported

|            | APIC Analysis<br>Only | APIC and<br>Pentium® | APIC and<br>Pentium® Pro |

|------------|-----------------------|----------------------|--------------------------|

| HP 16550A* | one card              | two cards            | two cards                |

| HP 16554A* | one card              | three cards          | three cards              |

| HP 16555A* | one card              | three cards          | three cards              |

| HP 16556A* | one card              | three cards          | three cards              |

\*Requires HP 16500B Mainframe with software version v3.04 or higher

The preprocessor interface provides the physical connection between the target system and the logic analyzer. The configuration software on the flexible disk sets up the logic analyzer for compatibility with the preprocessor interface.

For more information on the supported logic analyzers, microprocessors, or other preprocessor interfaces, refer to the appropriate reference manuals for those products.

®Pentium is a registered trademark of Intel Corporation.

E2467A Intel APIC Bus Preprocessor Interface

ii

### Introduction The HP E2467A Preprocessor Interface—At a Glance

### HP E2467A Preprocessor Interface Assembly

E2467A Intel APIC Bus Preprocessor Interface

### iii

### In This Book

This book is the user's guide for the HP E2467A Preprocessor Interface. It assumes that you have a working knowledge of the logic analyzer used and the APIC bus.

This user's guide is organized into three chapters:

Chapter 1 explains how to attach the preprocessor to the target system and how to configure the logic analyzer for analysis.

Chapter 2 provides reference information on the format specification and symbols configured by the preprocessor interface software and information about the inverse assembler and status encoding.

Chapter 3 contains reference information on the preprocessor interface hardware, including the characteristics and signal mapping for the preprocessor interface.

E2467A Intel APIC Bus Preprocessor Interface

iv

### Table of Contents

### **1** Setting Up the Preprocessor Interface

Equipment Configurations 1–3 Equipment Supplied 1–3 Minimum Equipment Required 1–4 Standalone APIC Interface 1–4 APIC Interface with HP E2457A Pentium® Preprocessor Interface for State and Timing Analysis of Pentium® 1–4 APIC Interface with HP E2466B Preprocessor Interface for State and Timing Analysis of Pentium® Pro 1–5

Connecting to the target system 1-6

To power up or power down 1–6 To connect the APIC preprocessor for standalone APIC Bus analysis 1–7 To connect to the target system through the Pentium® or Pentium® Pro preprocessor interface 1–9

Connecting to the Logic Analyzer 1–11

To connect to the HP 16550A analyzer 1–12 To connect to the HP 16554A/55A/56A analyzers 1–13

Loading the Preprocessor Interface Software 1-14

To load the configuration and inverse assembler into the HP 16500B mainframe 1-14

E2467A Intel APIC Bus Preprocessor Interface

Table of Contents

### 2 Analyzing the APIC Bus

Displaying Information 2–3

To display the format specification 2–3 To display the configuration symbols 2–5 To display captured state data 2–12

Using the Inverse Assembler 2–13

Inverse Assembler Exception Messages 2–15 Protocol violations 2–15

Triggering Hints 2–16

To capture actual APIC Bus serial line signals 2–17 To trigger on Delivery Mode 2–17 To trigger on a particular vector 2–17 To trigger on multiple criterion 2–18 To trigger on an APIC exception message 2–18 To trigger on Data in Remote Read message 2–18

### **3** Preprocessor Interface Hardware Reference

Operating Characteristics 3–3 Theory of Operation and Clocking 3–5 Signal-to-Connector Mapping 3–5 Circuit Board Dimensions 3–12 Repair Strategy 3–13

E2467A Intel APIC Bus Preprocessor Interface

vi

### A If You Have a Problem

Analyzer Problems A–3

Intermittent data errors A-3 No activity on activity indicators A-4 No trace list display A-4

Preprocessor Problems A-5

Target system will not boot up A-5 Erratic trace measurements A-6 Capacitive loading A-6

Inverse Assembler Problems A-7

No inverse assembly or incorrect inverse assembly A–7 Inverse assembler will not load or run A–8  $\,$

Intermodule Measurement Problems A-9

An event wasn't captured by one of the modules A-9

Messages A-10

"... Inverse Assembler Not Found" A-10

"No Configuration File Loaded" A-10

"Selected File is Incompatible" A-10

"Measurement Initialization Error" A-11

"Slow or Missing Clock" A-12

"Time from Arm Greater Than 41.93 ms" A-12

"Waiting for Trigger" A-12

E2467A Intel APIC Bus Preprocessor Interface

vii

E2467A Intel APIC Bus Preprocessor Interface

viii

Setting Up the Preprocessor Interface

1

# Setting Up the Preprocessor Interface

This chapter explains how to set up the HP E2467A Preprocessor Interface hardware and software, configure the preprocessor, and connect the preprocessor to supported logic analyzers.

E2467A Intel APIC Bus Preprocessor Interface

### **Equipment Configurations**

This section lists the equipment supplied with the HP E2467A Preprocessor Interface, and the equipment required for the various measurement configurations. It also includes information about the logic analyzers supported by the HP E2467A.

### **Equipment Supplied**

The HP E2467A Preprocessor Interface consists of the following equipment:

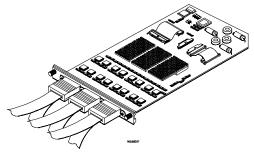

- The preprocessor interface hardware, which includes the preprocessor circuit card.

- The HP 16500B inverse assembler software and configuration files on a 3.5-inch disk.

- The HP 16505A Prototype Analyzer inverse assembler software and configuration files, for use with the HP E2467A.

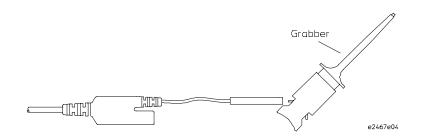

- Three flying leads, to attach the preprocessor interface to the target system. Included with the flying leads are four grabbers and three ground leads.

- This User's Guide.

E2467A Intel APIC Bus Preprocessor Interface

### Minimum Equipment Required

The HP E2467A Preprocessor Interface can be used in three different configurations: as a stand-alone APIC Bus interface, as an APIC interface with an HP E2457A Pentium® Preprocessor Interface, or as an APIC interface with an HP E2466A/B Pentium® Pro Preprocessor Interface. The part numbers and equipment are listed for each of these configurations.

### **Standalone APIC Interface**

When used as an APIC interface, the preprocessor interface provides state analysis of the target system APIC bus. The following equipment is required for this configuration:

- The HP E2467A Preprocessor Interface, which includes the circuit card hardware and the configuration files and inverse assembler software.

- The flying leads. For some target systems, the grabbers are also required.

- An HP 16500B mainframe.

- One of the logic analyzers listed in the table at the end of this section.

# APIC Interface with HP E2457A Pentium $\ensuremath{\mathbb{R}}$ Preprocessor Interface for State and Timing Analysis of Pentium $\ensuremath{\mathbb{R}}$

When used with the HP E2457A preprocessor interface for state and timing analysis of Pentium® target systems, the following equipment is required:

- The HP E2467A Preprocessor Interface.

- The HP E2457A Preprocessor Interface hardware, which includes the combined configuration files and the inverse assembler software.

- The flying leads (grabbers not needed).

- An HP 16500B mainframe.

- One of the logic analyzers listed in the table at the end of this section.

E2467A Intel APIC Bus Preprocessor Interface

# APIC Interface with HP E2466B Preprocessor Interface for State and Timing Analysis of Pentium® Pro

When used with the HP E2466B Preprocessor Interface for state and timing analysis of Pentium<sup>®</sup> Pro target systems, the following is required:

- The HP E2467A Preprocessor Interface.

- The HP E2466B Preprocessor Interface hardware, which includes the combined configuration files and the inverse assembler software.

- The flying leads (grabbers not needed).

- An HP 16500B mainframe.

- One of the logic analyzers listed in the following table.

#### Logic Analyzer Characteristics

| Logic Analyzer | Channel<br>Count | State Speed | Timing Speed | Memory<br>Depth |

|----------------|------------------|-------------|--------------|-----------------|

| 16550A         | 102/card         | 100 MHz     | 250 MHz      | 4 k states      |

| 16554A         | 68/card          | 70 MHz      | 125 MHz      | 512 k states    |

| 16555A         | 68/card          | 110 MHz     | 250 MHz      | 1 M states      |

| 16556A         | 68/card          | 100 MHz     | 200 MHz      | 1 M states      |

### Logic Analyzers Supported

| Logic Analyzer | APIC Analysis<br>Only | APIC and<br>Pentium® | APIC and<br>Pentium® Pro |

|----------------|-----------------------|----------------------|--------------------------|

| HP 16550A*     | one card              | two cards            | two cards                |

| HP 16554A*     | one card              | three cards          | three cards              |

| HP 16555A*     | one card              | three cards          | three cards              |

| HP 16556A*     | one card              | three cards          | three cards              |

\*Requires HP 16500B Mainframe with software version v3.04 or higher

E2467A Intel APIC Bus Preprocessor Interface

### Connecting to the target system

Setting up the preprocessor interface hardware consists of the following major steps:

- Turn off power to the target system and the logic analyzer.

- If you are doing standalone APIC analysis, use the flying leads to connect the preprocessor interface to the target system.

- If you are using the APIC preprocessor interface with a Pentium® or Pentium® Pro preprocessor interface, connect the Pentium® or Pentium® Pro preprocessor interface to the target system, then use the flying leads to connect the APIC preprocessor interface to the Pentium® or Pentium® Pro preprocessor interface.

The following sections cover these topics in detail

### To power up or power down

When powering up, the logic analyzer must be powered up first, and then the target system. The logic analyzer provides the power to the active circuits on the preprocessor interface; unpowered circuits may cause improper operation of the target system.

When powering down, the target system should be powered down first, and then the logic analyzer.

E2467A Intel APIC Bus Preprocessor Interface

# To connect the APIC preprocessor for standalone APIC Bus analysis

If you are performing only APIC Bus analysis, you must connect the APIC preprocessor interface directly to the APIC signals on the target system.

- 1 To prevent equipment damage, remove power from both the logic analyzer and the target system.

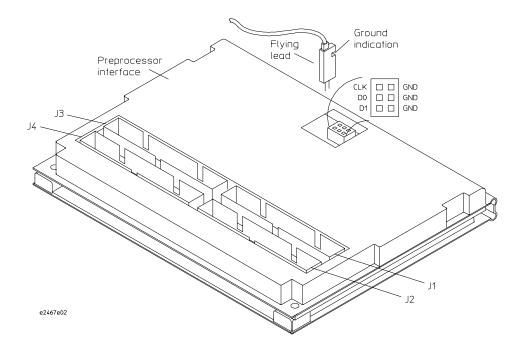

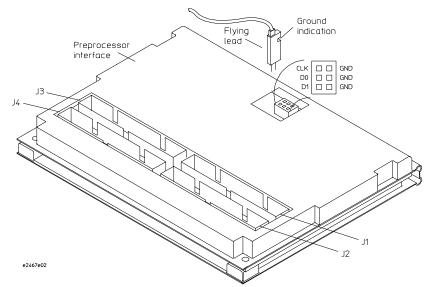

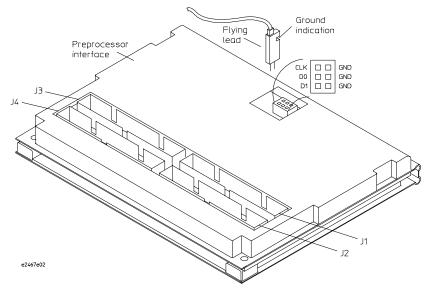

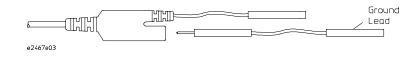

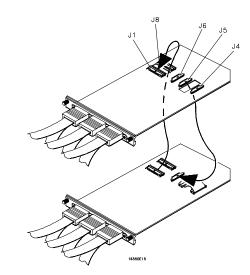

- **2** Connect the three flying leads to the six-pin APIC signal connector on the APIC preprocessor interface.

Ensure that you do not cross the signals and the grounds. The three active signals (CLK, D0, and D1) are located to the interior of the circuit board, and the three grounds are on the outside edge. The ground side of the flying lead connector has a notch (see below). Serious damage to the target system and/or the circuit board can result from improper connection.

Connecting the Flying Leads to the APIC Connector

CAUTION

E2467A Intel APIC Bus Preprocessor Interface

Connecting to the target system To connect the APIC preprocessor for standalone APIC Bus analysis

**2** Locate the following signals on the target system: APIC Clk, D1, and D0. If necessary, use the grabbers to connect to each signal on the target system.

**Optional Grabber**

**3** Connect a ground lead from one of the flying leads to an appropriate ground point on the target system. If necessary, use a grabber.

**Ground Lead**

E2467A Intel APIC Bus Preprocessor Interface

# To connect to the target system through the Pentium® or Pentium® Pro preprocessor interface

If you are using the APIC bus preprocessor interface with the Pentium® or Pentium® Pro preprocessor interface, you can connect to the APIC signals through the Pentium® or Pentium® Pro preprocessor interface.

- 1 To prevent equipment damage, remove power from both the logic analyzer and the target system.

- 2 Use the directions in the Pentium® or Pentium® Pro User's Guide to connect the Pentium® or Pentium® Pro preprocessor interface to the target system.

- **3** Connect the three flying leads to the six-pin APIC signal connector on the APIC preprocessor interface.

CAUTIONEnsure that you do not cross the signals and the grounds. The three active<br/>signals (CLK, D0, and D1) are located to the interior of the circuit board, and<br/>the three grounds are on the outside edge. The ground side of the flying lead<br/>connector has a notch. Serious damage to the target system and/or the<br/>circuit board can result from improper connection.

Connecting the Flying Leads to the APIC Connector

E2467A Intel APIC Bus Preprocessor Interface

Connecting to the target system

To connect to the target system through the Pentium® or Pentium® Pro preprocessor interface

- 4 Locate the following signals on the Pentium® or Pentium® Pro preprocessor interface: APIC Clk, D1, and D0 (see illustration in appropriate User's Guide to find the headers where these signals are located). Use the flying leads to connect each signal to the appropriate pin on the the Pentium® or Pentium® Pro preprocessor interface.

- 5 Connect a ground lead from one of the flying leads to a ground pin on the Pentium® or Pentium® Pro preprocessor interface header.

#### Ground Lead

6 Refer to the user's guide that came with the Pentium® or Pentium® Pro for instructions on connecting the APIC Bus Preprocessor to the logic analyzer. Use the configuration files included with the Pentium® or Pentium® Pro preprocessor.

# Connecting to the Logic Analyzer

The following sections show the connections between the logic analyzer pod cables and the connectors on the preprocessor interface. Use the appropriate section for your logic analyzer. The configuration file names for each logic analyzer are located at the bottom of the connection diagrams.

E2467A Intel APIC Bus Preprocessor Interface

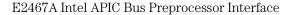

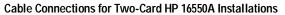

### To connect to the HP 16550A analyzer

Use the table below to connect the preprocessor to the HP 16550A logic analyzer.

| HP 16550A<br>Expansion<br>Card | Expansion<br>Card<br>Pod 6 | Expansion<br>Card<br>Pod 5 | Expansion<br>Card<br>Pod 4 | Expansion<br>Card<br>Pod 3 | Expansion<br>Card<br>Pod 2 | Expansion<br>Card<br>Pod 1 |

|--------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| HP E2467A<br>Connector         | not used                   |

| HP 16550A<br>Master<br>Card    | Master Card<br>Pod 6       | Master Card<br>Pod 5       | Master Card<br>Pod 4       | Master Card<br>Pod 3       | Master Card<br>Pod 2       | Master Card<br>Pod 1       |

| HP E2467A<br>Connector         | not used                   | not used                   | J4 DATA_B                  | J3 DATA_B                  | J2 DATA                    | J1 DATA<br>clk ↑           |

### Configuration File

Use configuration file CAPICA01 if you are only using two pods with the HP 16550A logic analyzer, and CAPICA02 if you are using four pods with the HP 16550A logic analyzer. You must use the correct configuration file for the number of pods used, since the preprocessor interface auto detects the number of connected pods and adjusts accordingly.

1 - 12

E2467A Intel APIC Bus Preprocessor Interface

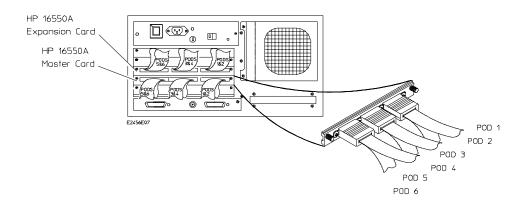

### To connect to the HP 16554A/55A/56A analyzers

Use the table below to connect the preprocessor to the HP 16554A/55A/56A.

| HP 16554A/55A/56A<br>Exp. Card 1 | not used             |                      |                      |                      |  |

|----------------------------------|----------------------|----------------------|----------------------|----------------------|--|

| HP 16554A/55A/56A<br>Master Card | Master Card<br>Pod 4 | Master Card<br>Pod 3 | Master Card<br>Pod 2 | Master Card<br>Pod 1 |  |

| HP E2467A<br>Connector           | J4 DATA_B            | J3 DATA_B            | J2 DATA              | J1 DATA<br>clk ↑     |  |

HP 16554A/55A/56A Exp. Card 2 not used

**Configuration File**

Use configuration file CAPICA03 if you are only using two pods with the HP 16554A/55A/56A logic analyzer, and CAPICA04 if you are using four pods with the HP 16554A/55A/56A logic analyzer. You must use the correct configuration file for the number of pods used, since the preprocessor interface auto detects the number of connected pods and adjusts accordingly.

E2467A Intel APIC Bus Preprocessor Interface

### Loading the Preprocessor Interface Software

Configuring the logic analyzer consists of loading the software by inserting the floppy disk into the logic analyzer disk drive or HP 16505A Prototype Analyzer and loading the proper configuration file. The configuration file you use is determined by the logic analyzer you are using and whether or not you are using the HP 16505A Prototype Analyzer.

The HP 16505A Prototype Analyzer update disk provides HP 16505A-specific inverse assembler files and HP 16505A-specific configuration files. The HP 16505A configuration files assist in triggering on APIC messages. These configuration files are located in the /hp16505/config/apicbus directory, and have the same prefix names as the 16500B config files.

### To load the configuration and inverse assembler into the HP 16500B mainframe

The first time you set up the preprocessor interface, make a duplicate copy of the master disk. For information on duplicating disks, refer to the reference manual for your logic analyzer.

For logic analyzers with a hard disk, you might want to create a directory such as APIC on the hard drive and copy the contents of the "HP 16500B Logic Analyzer Configs" floppy onto the hard drive. You can then use the hard drive for loading files, instead of the floppy disk drives listed in step 2.

- 1 Insert the "HP 16500B Logic Analyzer Configs" floppy disk in the front disk drive of the logic analyzer.

- 2 Go to the System Flexible Disk menu.

- **3** Configure the menu to load.

- 4 Use the knob to select the appropriate configuration file.

Choosing the correct configuration file depends on which analyzer you are using, and whether you are also using a Pentium® or Pentium® Pro preprocessor interface with the APIC preprocessor interface. The

E2467A Intel APIC Bus Preprocessor Interface

configuration files are shown with the logic analyzer connection tables, and are also in the table below.

- 5 Select the appropriate analyzer (such as "100/500 MHz LA") for the load.

- **6** Execute the load operation on the menu to load the file into the logic analyzer.

The logic analyzer is configured for APIC analysis by loading the appropriate configuration file. Loading this file also automatically loads the correct inverse assembler.

| A I               | 4/500 4                         | T                             |                      |

|-------------------|---------------------------------|-------------------------------|----------------------|

| Analyzer<br>Model | 16500 Analyzer<br>Description   | Type of Analysis              | Configuration File   |

| 16550A            | 100 MHZ STATE<br>500 MHZ TIMING | Two-pod APIC<br>Four-pod APIC | CAPICA01<br>CAPICA02 |

| 16554A            | 0.5M SAMPLE<br>70/250 MHz LA    | Two-pod APIC<br>Four-pod APIC | CAPICA03<br>CAPICA04 |

| 16555A            | 1.0M SAMPLE<br>110/250 MHz LA   |                               |                      |

| 16556A            | 1.0M SAMPLE<br>100/400 MHz LA   |                               |                      |

### Logic Analyzer Configuration Files

E2467A Intel APIC Bus Preprocessor Interface

Loading the Preprocessor Interface Software To load the configuration and inverse assembler into the HP 16500B mainframe

### APIC Configuration Files and Inverse Assembler

| Analyzer<br>Model | Type of Analysis | Configuration File | Inverse Assembler |

|-------------------|------------------|--------------------|-------------------|

| 16550A            | Two-pod APIC     | CAPICA01           | iapic2            |

|                   | Four-pod APIC    | CAPICA02           | iapic4            |

| 16554A/55A        | Two-pod APIC     | CAPICA03           | iapic2            |

| /56A              | Four-pod APIC    | CAPICA04           | iapic4            |

E2467A Intel APIC Bus Preprocessor Interface

Analyzing the APIC Bus

# Analyzing the APIC Bus

This chapter describes how to display configuration information and preprocessor interface data, gives label and symbol encodings for the status field, and provides information about the inverse assembler.

E2467A APIC Bus Preprocessor Interface

### **Displaying Information**

This section describes how to display logic analyzer configuration information, state and timing data captured by the preprocessor interface, and symbol information that has been set up by the preprocessor interface configuration software.

### To display the format specification

• Select the format specification menu for your logic analyzer.

The APIC Bus configuration files contain predefined format specifications. These format specifications include all labels for monitoring the APIC bus.

Chapter 3 of this guide contains a table that lists the signals for the APIC Bus preprocessor and on which pod and probe line the signal comes to the logic analyzer. Refer to this table and to the logic analyzer connection information for your analyzer in chapter 1 to determine where the signals should be on the format specification screen.

E2467A APIC Bus Preprocessor Interface

# **Example** The format specification display shown in the following figure is from the HP 16550A logic analyzer. Additional labels and pod assignments are listed off the screen. Select the "Labels" field and rotate the knob on the analyzer front panel to view additional signals. Select the "Pods" field and rotate the knob to view other pod-bit assignments. There may be some slight

differences in the display shown by your particular analyzer.

|          | Acqu | isition Mode                  | Master Clock<br>[(j†)+(K=1)] | Print Group Run<br>Symbols |

|----------|------|-------------------------------|------------------------------|----------------------------|

|          |      | Clock Inputs<br>Slot D Slot E | Pod E2 TTL<br>Master Clock   | Pod E1 TTL<br>Master Clock |

| + Labels | ·    | -<br>ĸĴ                       | 15 87 0                      | 15 87 0                    |

| ArbID    | -    | *,                            |                              | *****                      |

| Vector   | -    | *,                            |                              | **                         |

| Error    | +    | *.                            | ***                          | **                         |

| EOI      | -    | *.                            | *                            | **                         |

| C1Stat   | -    | *.                            | **                           | **                         |

| A Stat   | -    | *.                            | *****                        | **                         |

| AlStat   | -    | *.                            | ****** . ***                 | **                         |

| DestMo   | -    | *.                            | *                            | **                         |

Logic Analyzer Format Specification (two-pod logic analyzer)

| 100/500  | MHz L | A E Format 2                       | )                           | Print Run                  |

|----------|-------|------------------------------------|-----------------------------|----------------------------|

|          |       | uisition Mode<br>/4K Memory/100MHz | Master Clock<br>(J†)•(K=1)] | Symbols                    |

| + Pods   | •     | Clock Inputs<br>Slot D Slot E      | Pod E4 TTL<br>Master Clock  | Pod E3 TTL<br>Master Clock |

| + Labels | •     | MLKJ                               | 15 87 0                     | 15 87 0                    |

| ArbID    | -     | *.                                 |                             |                            |

| Vector   | -     | * .                                |                             |                            |

| Error    | +     | *.                                 |                             |                            |

| EOI      | -     | *.                                 |                             |                            |

| C1Stat   | -     | *.                                 |                             |                            |

| A Stat   | -     | *.                                 |                             |                            |

| AlStat   | -     | *.                                 |                             |                            |

| DestMo   | -     | * .                                |                             |                            |

Logic Analyzer Format Specification (four-pod logic analyzer)

2-4

E2467A APIC Bus Preprocessor Interface

### To display the configuration symbols

• Select the "Symbols" field on the format specification menu and then choose a label name from the "Label" pop-up. The logic analyzer will display the symbols associated with the label.

The HP E2467A configuration software sets up symbol tables on the logic analyzers. The tables contain alphanumeric symbols which identify APIC cycles. Labels simplify triggering on specific APIC Bus cycles. The label base in the symbols menu is set to hexadecimal to conserve space.

The number of bits depends on the logic analyzer you are using. For some of the listings, a four-pod logic analyzer uses twice as many bits as a two-pod logic analyzer. A two-pod logic analyzer uses each pod twice for each cycle, therefore it only uses half as many logic analyzer bits.

The first of the following tables describes the decode of the APIC Bus signals that are captured by the preprocessor. The second table lists the label and symbol encodings defined by the logic analyzer configuration software.

Under the heading "Polarity", negative means that the logic analyzer inverts the signal. Positive means that the logic analyzer does not invert the signal.

E2467A APIC Bus Preprocessor Interface

### Signal/Label List

| abel Name   | Polarity     | Number of bits<br>2/4-pod | Description                        |

|-------------|--------------|---------------------------|------------------------------------|

| PIC Message | Signals      |                           |                                    |

| vrbID       | negative     | 7                         | Arbitration ID                     |

| ector       | negative     | 11                        | Interrupt Vector                   |

| ror         | positive     | 6                         | Error number                       |

| )           | negative     | 4                         | EOI Status                         |

| Stat        | negative     | 5                         | Checksum                           |

| Stat        | negative     | 8                         | A status                           |

| Stat        | negative     | 11                        | A1 status                          |

| stMo        | negative     | 5                         | Destination Mode                   |

| live        | negative     | 7                         | Delivery mode                      |

| vel         | negative     | 5                         | Level (physical or logical)        |

| gge         | negative     | 5                         | Trigger (edge or level)            |

| or          | negative     | 7                         | Priority Arbitration ID            |

| ID          | negative     | 10/14                     | Lowest Priority Tie Arbitration ID |

| itat        | negative     | 5/8                       | S status                           |

| Stat        | negative     | 5/8                       | Remote Read Data checksum          |

| Stat        | negative     | 8/10                      | A2 status                          |

| stID        | negative     | 11/11                     | Destination ID                     |

| ata         | negative     | 19/22                     | Upper 16 bits of data              |

| ata         | negative     | 19/22                     | Lower 16 bits of data              |

| ffered APIC | Signals      |                           |                                    |

| CD1         | positive     |                           | APIC D1                            |

| CD0         | positive     |                           | APIC D0                            |

| erse assem  | bler symbols |                           |                                    |

| DR          | positive     | 32                        | unused                             |

| ATA         | negative     | 32                        | signals from pods 1 and 2          |

| ATA_B       | negative     | 32                        | signals from pods 3 and 4          |

| AT          | positive     | 32                        | status signals from pods 1 and 2   |

2-6

E2467A APIC Bus Preprocessor Interface

### Displaying Information **To display the configuration symbols**

The following table lists the label and symbol encodings defined by the logic analyzer configuration software.

The base is shown with the values in binary.

### **APIC Bus Symbols**

| LABEL = Signals               | Symbol     | Value        |

|-------------------------------|------------|--------------|

| ArbID = Valid, Cycle, ArbID   | PIC 0      | 0 10 0000    |

|                               | PIC 1      | 0 10 0001    |

|                               | PIC 2      | 0 10 0010    |

|                               | PIC 3      | 0 10 0011    |

|                               | PIC 4      | 0 10 0100    |

|                               | PIC 5      | 0 10 0101    |

|                               | PIC 6      | 0 10 0110    |

|                               | PIC 7      | 0 10 0111    |

|                               | PIC 8      | 0 10 1000    |

|                               | PIC 9      | 0 10 1001    |

|                               | PIC 10     | 0 10 1010    |

|                               | PIC 11     | 0 10 1011    |

|                               | PIC 12     | 0 10 1100    |

|                               | PIC 13     | 0 10 1101    |

|                               | PIC 14     | 0 10 1110    |

|                               | PIC 15     | 0 10 1111    |

| Vector = Valid, Cycle, Vector | Vector Oh  | 0 10 0000000 |

|                               | Vector 1h  | 0 10 0000001 |

|                               | Vector 2h  | 0 10 0000010 |

|                               | :          | :            |

|                               | Vector nh  | 0 10 n       |

|                               | :          | :            |

|                               | Vector FFh | 0 10 1111111 |

E2467A APIC Bus Preprocessor Interface

| Error = Valid, Error, Cycle                                     | Arbitration ID<br>Idle Cycle Error<br>Post Amble Error<br>Priority Cycle<br>Tie ID Ard Cycle<br>unknown | 1 001 01<br>1 010 01<br>1 011 01<br>1 100 01<br>1 110 01<br>1 111 01                                                                                                  |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EOI = Valid, EOI, Cycle                                         | EOI Cycle<br>Normal Cycle                                                                               | 0 1 10<br>0 0 10                                                                                                                                                      |

| C1Stat = Valid, C1Stat, Cycle                                   | Checksum 3<br>Checksum 2<br>Checksum 1<br>Checksum 0                                                    | 0 00 10<br>0 01 10<br>0 10 10<br>0 11 10                                                                                                                              |

| A Stat = Valid, A Stat,<br>Delivery Mode, Cycle                 | CS OK, no foc<br>CS OK, focus<br>CS OK<br>CS Error<br>Error                                             | 0 00 001 10<br>0 10 001 10<br>0 00 xxx 10<br>0 11 xxx 10<br>0 01 xxx 10                                                                                               |

| A1Stat = Valid, EOI, A Stat,<br>A1Stat, Delivery Mode,<br>Cycle | Go for LP Arb<br>End and Retry<br>Retry<br>Accept Error<br>Accepted<br>Error<br>Bus Not Driven          | 0 0 00 11 001 10 (low priority)<br>0 0 00 10 001 10 (low priority)<br>0 1 00 11 000 10<br>0 1 00 0x xxx 10<br>0 x 00 10 xxx 10<br>0 0 1x x0 xxx 10<br>0 x xx xx xx 10 |

| DestMo = Valid, EOI,<br>Destination Mode,<br>Cycle              | Logical<br>Physical                                                                                     | 0 0 1 10<br>0 0 0 10                                                                                                                                                  |

| Delive = Valid, EOI, Delivery<br>Mode, Cycle                    | Fixed<br>Lowest Priority<br>SMI<br>Remote Read<br>NMI<br>INIT<br>Start Up<br>reserved                   | 0 0 000 10<br>0 0 001 10<br>0 0 010 10<br>0 0 011 10<br>0 0 100 10<br>0 0 101 10<br>0 0 101 10<br>0 0 110 10<br>0 0 111 10                                            |

| Level = Valid, EOI, Level, Cycle                                | Assert<br>De-assert                                                                                     | 0 0 1 10<br>0 0 0 10                                                                                                                                                  |

2-8

E2467A APIC Bus Preprocessor Interface

### Displaying Information To display the configuration symbols

| Trigge = Valid, EOI, Trigger,<br>Cycle | Level<br>Edge                             | 0 0 1 10<br>0 0 0 10                                          |

|----------------------------------------|-------------------------------------------|---------------------------------------------------------------|

| Prior = Valid, Cycle, Prior            | PIC 0<br>PIC 1<br>PIC 2<br>PIC 3<br>PIC 4 | 0 10 0000<br>0 10 0001<br>0 10 0010<br>0 10 0011<br>0 10 0100 |

|                                        | PIC 5<br>PIC 6<br>PIC 7                   | 0 10 0101<br>0 10 0110<br>0 10 0111                           |

|                                        | PIC 8<br>PIC 9<br>PIC 10<br>PIC 11        | 0 10 1000<br>0 10 1001<br>0 10 1010<br>0 10 1011              |

|                                        | PIC 12<br>PIC 13<br>PIC 14<br>PIC 15      | 0 10 1100<br>0 10 1101<br>0 10 1110<br>0 10 1111              |

E2467A APIC Bus Preprocessor Interface

| TieID = Valid, Delivery Mode,<br>Cycle, TieID (two-pod) | PIC 0      | two-pod<br>0 001 01 0000       | four-pod<br>  0 0000 00 11 001 10 |

|---------------------------------------------------------|------------|--------------------------------|-----------------------------------|

| TieID = Valid, TieID, A Stat,                           | PIC 1      | 0 001 01 0001                  | 0 0001 00 11 001 10               |

| A1Stat, Delivery Mode,                                  | PIC 2      | 0 001 01 0010                  | 0 0010 00 11 001 10               |

| Cycle (four-pod)                                        | PIC 3      | 0 001 01 0011                  | 0 0011 00 11 001 10               |

|                                                         |            |                                |                                   |

|                                                         | PIC 4      | 0 001 01 0100                  | 0 0100 00 11 001 10               |

|                                                         | PIC 5      | 0 001 01 0101                  | 0 0101 00 11 001 10               |

|                                                         | PIC 6      | 0 001 01 0110                  | 0 0110 00 11 001 10               |

|                                                         | PIC 7      | 0 001 01 0111                  | 0 0111 00 11 001 10               |

|                                                         |            |                                |                                   |

|                                                         | PIC 8      | 0 001 01 1000                  | 0 1000 00 11 001 10               |

|                                                         | PIC 9      | 0 001 01 1001                  | 0 1001 00 11 001 10               |

|                                                         | PIC 10     | 0 001 01 1010                  | 0 1010 00 11 001 10               |

|                                                         | PIC 11     | 0 001 01 1011                  | 0 1011 00 11 001 10               |

|                                                         | DTG 10     | 0 001 01 1100                  |                                   |

|                                                         | PIC 12     | 0 001 01 1100                  | 0 1100 00 11 001 10               |

|                                                         | PIC 13     | 0 001 01 1101                  | 0 1101 00 11 001 10               |

|                                                         | PIC 14     | 0 001 01 1110<br>0 001 01 1111 | 0 1110 00 11 001 10               |

|                                                         | PIC 15     | 0 001 01 1111                  | 0 1111 00 11 001 10               |

| S Stat (data valid) = Valid,                            |            | two-pod   four                 | -pod                              |

| Cycle, S Stat (two-pod)                                 | Valid      | 0 01 11   0 11                 | 011 10                            |

| S Stat (data valid) = Valid,                            | Invalid    | 0 01 00   0 00                 | 011 10                            |

| S Stat, Delivery Mode,                                  | Invalid    | 0 01 01   0 01                 | 011 10                            |

| Cycle (four-pod)                                        | Invalid    | 0 01 10   0 10                 | 011 10                            |

|                                                         |            | x xx xx x x xx                 | XXX XX                            |

| C2Stat = Valid, Cycle, C2Stat                           |            | two-pod   four                 | -poq-                             |

| (two-pod)                                               | Checksum 0 | -                              | 011 10                            |

| C2Stat = Valid, C2Stat,                                 | Checksum 1 | 0 01 01 0 01                   | 011 10                            |

| Delivery Mode,                                          | Checksum 2 | 0 01 10 0 10                   | 011 10                            |

| Cycle (four-pod)                                        | Checksum 3 | 0 01 11 0 11                   | 011 10                            |

|                                                         |            | x xx xx x x xx                 | XXX XX                            |

| A2Stat = Valid, A2Stat,                                 |            | two-pod                        | four-pod                          |

| Delivery Mode,                                          | Accept     | -                              | $0 \ 10 \ 00 \ 011 \ 01$          |

| Cycle (ťwo-pod)                                         | Error      |                                | 0 11 00 011 01                    |

| ADState Valid ADState A1Stat                            | Error      |                                | 0 0x 00 011 01                    |

| A2Stat = Valid, A2Stat, A1Stat,<br>Delivery Mode,       |            |                                | O OX OO OIT OI                    |

| Cycle (four-pod)                                        |            |                                |                                   |

|                                                         | 1          | I                              |                                   |

2-10

E2467A APIC Bus Preprocessor Interface

### Displaying Information To display the configuration symbols

| DestID = Valid, Cycle,<br>Destination ID (two-pod   | DestID Oh              | two-pod<br>0 01 00000000            | four-pod<br>0 0000000 10         |

|-----------------------------------------------------|------------------------|-------------------------------------|----------------------------------|

| DestID = Valid, Destination ID,<br>Cycle (four-pod) | DestID 1h<br>DestID 2h | 0 01 00000001<br>0 01 00000010<br>: | 0 0000001 10<br>0 00000010 10    |

|                                                     | DestID nh<br>:         | 0 01 n<br>:                         | 0 n 10<br>:                      |

|                                                     | DestID FFh             | 0 01 11111111                       | 0 11111111 10                    |

| UData = Valid, Data, Cycle<br>(two-pod)             |                        | two-pod<br>0 (16 data) 01           | four-pod<br>  0 (16 data) xxx 10 |

| UData = Valid, Data,<br>Delive, Cycle<br>four-pod)  |                        | x (16 data) xx                      | x (16 data) xxx xx               |

| LData = Valid, Data, Cycle<br>(two-pod)             |                        | two-pod<br>0 (16 data) 00           | four-pod<br>  0 (16 data) xxx 10 |

| LData = Valid, Data,<br>Delive, Cycle<br>(four-pod) |                        | x (16 data) xx                      |                                  |

E2467A APIC Bus Preprocessor Interface

### To display captured state data

### • Select the Listing Menu for your logic analyzer.

The logic analyzer displays captured data in the Listing Menu. The inverse assembler processes the captured data in a transaction-based format.

If your trace listing doesn't appear to be correct (capturing the same RAM address twice, for example), make sure the preprocessor interface hardware is configured for state analysis. The "Invasm Options" field will appear at the top of the Listing Menu screen when the logic analyzer is configured for state analysis. See Chapter 1 to review the hardware configuration, correct it if needed, and then run the trace again.

The following figure shows the Listing Menu display for the HP 16550A logic analyzer using the two-pod inverse assembler.

| (100/500MHz LA E)     Listing 2     (Invesm Options)     (Print)     Run       Markers     Acquisition Time       Off     18 Jun 1996 14:26:42 |                                                                                                                                                                                                                                                                                                                                                              |                       |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Label><br>Base>                                                                                                                                | APIC Message Decoder v3.ad<br>Hex (except cycles)                                                                                                                                                                                                                                                                                                            | ArbID Ve<br>Symbol Sy |  |  |  |

| 6                                                                                                                                              | Message: init                                                                                                                                                                                                                                                                                                                                                | PIC 0 Ve              |  |  |  |

| 8                                                                                                                                              | Arb'ID : 0<br>Hodes : DM=physical L=assert TM=level<br>Vector : 00 (ignored)<br>Destin : 0F (Apic ID: F)<br>Chksum : 0<br>Stat A : CS okay<br>Stat A: accepted<br>Message: init deasert<br>Arb ID : 0<br>Hodes : DM=physical L=deassert TM=level<br>Vector : 00 (ignored)<br>Destin : 0F (Apic ID: F)<br>Chksum : 0<br>Stat A : CS okay<br>Stat A!: accepted | PIC O Ve              |  |  |  |

Logic Analyzer Listing Menu

E2467A APIC Bus Preprocessor Interface

Example

## Using the Inverse Assembler

This section discusses the general output format of the inverse assembler, and any APIC-specific information you will need.

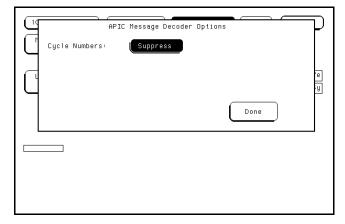

The APIC inverse assembler supports filter options based on Cycle number. You can Show or Suppress the second and third cycles.

The next few paragraphs describe the general output format of the inverse assembler.

#### **Numeric Format**

For data, the numeric output from the inverse assembler is in hexadecimal format. All other numbers are in decimal format.

E2467A APIC Bus Preprocessor Interface

2 - 13

#### Show/Suppress

The Suppress/Show settings determine whether the second and third cycles are shown or suppressed on the logic analyzer display. The Show/Suppress settings do not affect the data which is stored by the logic analyzer, they only affect whether that data is displayed or not. The same data can be examined later with different settings, for different analysis requirements.

#### Filter Menu

If the X or O pattern markers are turned on, and the designated pattern is found in a state that has been Suppressed with display filtering, the following message will appear on the logic analyzer display: "X (or O) pattern found, but state is suppressed."

E2467A APIC Bus Preprocessor Interface

### Inverse Assembler Exception Messages

APIC bus messages do not have a way of uniquely identifying a message start. It is possible to start interpreting a message in the middle of a message stream with incorrect results. The preprocessor hardware attempts to track the APIC messages and look for patterns to uniquely identify an APIC message. When it doesn't see an expected pattern, it is flagged as an exception, the information captured to that point is sent to the logic analyzer, and the hardware begins looking for another possible message start.

#### **Protocol violations**

The preprocessor detects the following APIC Bus exceptions (defined as Error in symbol table):

**Arbitration ID Cycle** Defined as a logic high on D0 during arbitration ID cycles.

Idle Cycle defined as a logic high on D0 during the idle cycle.

**Post Amble Cycle** defined as a logic high on D0 during the post amble cycle.

**Priority Cycle** defined as a logic high on D0 during the priority ID cycles.

**Tie ID Arb Cycle** defined as a logic high on D0 during the lowest priority tie arbitration ID cycles.

When the preprocessor detects one of the above exception conditions, it aborts capturing the message and sends what information it had captured up to that point. The inverse assembler does not try to interpret the data, but only reports which exception was detected. The defined symbols can be used to interpret what was captured before the message; however, be aware that the exception occurred before the complete message was captured and may contain information from the last successfully captured APIC message.

The inverse assembler does not attempt to do a complete job of detecting protocol violations. Undetected protocol violations may cause the inverse assembler to display incorrect results.

E2467A APIC Bus Preprocessor Interface

## **Triggering Hints**

To trigger on APIC message events, it is necessary to know which configuration, either 2 pod or 4 pod, the preprocessor is operating on. When used with a Pentium® or Pentium® Pro preprocessor interface, it is a two-pod configuration. The configuration determines on which cycle the APIC message information is sent, as shown in the following table:

| Cycle | 2 Pod                                                                                                                           | 4 Pod                                                                                                                                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ArbID<br>EOI<br>Vector/register<br>Dest Mode<br>Level<br>Trigger<br>Delivery Mode<br>Checksum<br>A Status<br>A1 Status<br>Error | ArbID<br>EOI<br>Vector/register<br>Dest Mode<br>Level<br>Trigger<br>Delivery Mode<br>Checksum<br>A Status<br>A1 Status<br>Error<br>Priority ID<br>LP Arb Tie ID<br>S Status<br>Checksum 2<br>Status<br>A2 Status<br>Destination ID<br>Upper Data word |

| 2     | Priority ID<br>LP Arb Tie ID<br>S Status<br>Checksum 2<br>Status<br>A2 Status<br>Destination ID<br>Upper Data word              | Lower Data word                                                                                                                                                                                                                                       |

| 3     | Lower Data Word                                                                                                                 |                                                                                                                                                                                                                                                       |

2-16

E2467A APIC Bus Preprocessor Interface

The 16505A Protocol Analyzer configuration files have the above groups assigned to three of the patterns to simplify setting up triggering. The HP 16500B does not have the the same grouping capability and hence, has all of the labels associated with each trigger pattern.

### To capture actual APIC Bus serial line signals

All messages sent by the APIC preprocessor are qualified by a high K clock. This is set up as the default mode in the format section. Using the K high qualifier to store messages ensures that the memory is filled with only APIC messages. The preprocessor also passes through the APIC serial signals on the first pod. To capture the serial bus events, the K high qualifier in the format section should be turned off. This will capture data on every APIC clock cycle, filling the data memory with everything, including the long gaps between APIC messages.

### To trigger on Delivery Mode

The delivery mode message types are defined in the Delive symbol. Select the type of message type to trigger on under the Delive symbol and set the other symbols to 'don't cares' (usually defined as '----' under the symbol name). Set up the trigger menu sequencer level to "while storing anystate, trigger on "a", where "a" is the pattern defined in the first step.

### To trigger on a particular vector

Vector addresses are defined in the Vector symbol. The symbol has definitions for all of the vectors. The setup is the same as for Delivery mode as defined above.

### To trigger on multiple criterion

Triggering on multiple criterion is similar to the above with the caveat that one must pay attention to the configuration that is in use and how the criterion breaks out into cycles as shown in the above table. For example, to trigger on a Lowest Priority message type and a particular destination ID, the Delive symbol and the DestID symbol would be used. If a 4 pod configuration is being used, these two symbols could be combined into one pattern and the trigger sequence level would be set up as in the previous examples. However, if the 2 pod configuration is being used, the symbols would have to be assigned to two different patterns. The first trigger sequence level would be assigned to find the Delive symbol, and the second trigger sequence level would be assigned to find and trigger on the DestID symbol. Using the pre-defined patterns from the HP 16505A Protocol Analyzer simplifies setting up the patterns since the symbols are already grouped according to cycles.

### To trigger on an APIC exception message

APIC exception messages are those defined in the section on Inverse Assembler exception Messages. To trigger on an exception message, use the symbols defined in the Error label.

### To trigger on Data in Remote Read message

Remote read data is spread across multiple cycles in the preprocessor. To trigger on a particular data pattern, it will have to be broken into a trigger sequence. It will also be necessary to know whether two or four pods are being used, as this affects which cycle the data is on.

The data has been broken into upper and lower words, and labels have been defined to help with the setup. The labels are UData and LData, respectively.

In addition to the 16 bits for each word, there is also one bit for valid message and one bit for cycle number. In addition, the four-pod configuration also includes the three bits for delivery mode to help distinguish from random data.

It is informative to look at the Format setup to see how the bits are assigned in the label. Note that the signals are defined as inverted under the Format

E2467A APIC Bus Preprocessor Interface

#### Triggering Hints To trigger on Data in Remote Read message

setup to transform electrical values to logical values, as defined in the APIC sppecification.

A message is valid when the K clock is high. The cycle number for the two and four pod configuration is listed at the beginning of this section. Because of the inversion, the Valid bit and the Cycle bits also have to be inverted or the Format labels have to be changed to "+" to match how the data will be interpreted.

#### Example: Triggering on 0x12345678 using a four-pod configuration

Because the data is broken into upper and lower words, two symbols will have to be created and a trigger sequence used. The upper word, 0x1234, would occur on cycle 1 when the K clock is high. The lower word would appear on cycle 2 when the K clock is high. A remote read corresponds to logical 011.

Because cycle and K are active high, they become inverted in the UData and LData symbols. The symbols look like this:

UData (Valid, Data, Delive, Cycle) = 0 0001 0010 0011 0100 011 10 LData (Valid, Data, Delive, Cycle) = 0 0101 0110 0111 1000 011 01

E2467A APIC Bus Preprocessor Interface

E2467A APIC Bus Preprocessor Interface

Preprocessor Interface Hardware Reference

## Preprocessor Interface Hardware Reference

This chapter contains reference information on the HP2467A hardware including product, electrical, and environmental characteristics, signal mapping, a brief theory of operation, and repair information.

E2467A APIC Bus Preprocessor Interface

### **Operating Characteristics**

The following operating characteristics are not specifications, but are typical operating characteristics for the preprocessor interface.

#### **Product Characteristics**

| Microprocessors Supported              | Intel APIC Bus microprocessors. The HP E2467A can be used standalone for APIC bus analysis, or with Pentium® or Pentium® Pro preprocessor interfaces for APIC Bus and microprocessor analysis.                         |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package Supported                      | Any target system in which APIC Clk, D0, and D1 can be probed.                                                                                                                                                         |

| Accessories Supported                  | HP E2457A for Pentium® microprocessor and APIC<br>Bus analysis, HP E2466A/B for Pentium® Pro<br>microprocessor and APIC Bus analysis.                                                                                  |

| Logic Analyzer Required                | HP 16500B mainframe with HP 16550A, HP 16554A,<br>HP 16555A, or HP 16556A logic analyzer.                                                                                                                              |

| Number of Probes Used                  | Two or four 17-channel probes are required for inverse assembly.                                                                                                                                                       |

| Microprocessor Operations<br>Displayed | Arbitration ID, Interrupt Vector, Error Number, EOI<br>Status, Checksum, A Status, A1 Status, A2 Status, S<br>Status, Destination Mode, Destination ID, Delivery<br>Mode, Priority Arbitration ID, Level, and Trigger. |

| Additional Capabilities                | When used with the HP E2457A or HP E2466A/B preprocessor interfaces, the APIC Bus preprocessor interface can be used to cross-trigger the logic analyzer on APIC Bus cycles.                                           |

| Timing Analysis                        | None.                                                                                                                                                                                                                  |

| Electrical Characteristics             |                                                                                                                                                                                                                        |

| Power Requirements                     | 500 mA at +5VDC, supplied by the logic analyzer.                                                                                                                                                                       |

| Signal Line Loading                    | The HP E2467A Preprocessor Interface adds 100 KOhms and 8 pF to APIC Clk, D0, and D1.                                                                                                                                  |

| Maximum Clock Speed                    | 33 MHz Clock Input.                                                                                                                                                                                                    |

E2467A APIC Bus Preprocessor Interface

Preprocessor Interface Hardware Reference **Operating Characteristics**

#### **Environmental Characteristics**

| Temperature | Operating                                                                                                                | 0 to + 55 degrees C                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|             | Nonoperating                                                                                                             | +32 to +131 degrees F<br>-40 to + 75 degrees C<br>-40 to +167 degrees F |

| Altitude    | Operating<br>Nonoperating                                                                                                | 4,600 m (15,000 feet)<br>15,3000 m (50,000 feet)                        |

| Humidity    | Up to 90% noncondensing. Avoid sudden , extreme temperature changes which could cause condensation on the circuit board. |                                                                         |

E2467A APIC Bus Preprocessor Interface

### Theory of Operation and Clocking

The HP E2467A APIC Bus preprocessor captures the APIC serial messages and sends them to the logic analyzer in parallel to simplify triggering. It operates in either a 2-pod or a 4-pod configuration. It watches the bus, looking for a start of message as indicated by the PIC D0 signal going high (electrically low). It then tracks the signals, looking for expected patterns. After it has captured an entire message or detected an error condition, it sends the message up to the logic analyzer.

Messages sent to the logic analyzer are qualified with the K clock. When the K clock is high, the message is valid. Most messages will take more than one clock cycle to send the message to the logic analyzer. Therefore, the cycle number has been encoded on two bits on one of the pods.

The APIC serial line signals are passed through the HP E2467A preprocessor up to the logic analyzer. The APIC Clock is used as the master clock while the D1 and D0 signals appear on Pod One as signals 1 and 0, respectively.

All three signals (clock, D1, and D0) are buffered through the preprocessor.

#### Signal-to-Connector Mapping

The following table shows the electrical interconnections implemented with the preprocessor interface. Note that the signals to the logic analyzer are different for two-pod and four-pod logic analyzers, and that they depend on the cycle.

E2467A APIC Bus Preprocessor Interface

| Two-Pod Logic Analyzer Signal List |                      |                          |                |                                      |                                                  |                               |

|------------------------------------|----------------------|--------------------------|----------------|--------------------------------------|--------------------------------------------------|-------------------------------|

| Pod                                | 2x20<br>pin          | Analyzer<br>Bit          | APIC<br>Signal | Analyzer<br>Labels<br>Cycle 1        | Analyzer<br>Labels<br>Cycle 2                    | Analyzer<br>Labels<br>Cycle 3 |

| P1                                 | 3                    | CLK1                     |                | PICCLK                               | PICCLK                                           |                               |

| P1<br>P1<br>P1<br>P1               | 7<br>9<br>11<br>13   | D15<br>D14<br>D13<br>D12 |                | cycle<br>cycle<br>ArbID<br>ArbID     | cycle<br>cycle<br>DestID<br>DestID               | cycle<br>cycle                |

| P1<br>P1<br>P1<br>P1               | 15<br>17<br>19<br>21 | D11<br>D10<br>D9<br>D8   |                | ArbID<br>ArbID<br>Vector<br>Vector   | DestID<br>DestID<br>DestID<br>DestID             |                               |

| P1<br>P1<br>P1<br>P1               | 23<br>25<br>27<br>29 | D7<br>D6<br>D5<br>D4     |                | Vector<br>Vector<br>Vector<br>Vector | DestID<br>DestID<br>S Stat/TieID<br>S Stat/TieID |                               |

| P1<br>P1<br>P1<br>P1               | 31<br>33<br>35<br>37 | D3<br>D2<br>D1<br>D0     | D1<br>D0       | Vector<br>Vector<br>PICD1<br>PICD0   | C2Stat/TieID<br>C2Stat/TieID<br>PICD1<br>PICD0   |                               |

Two-Pod Logic Analyzer Signal List

E2467A APIC Bus Preprocessor Interface

#### Preprocessor Interface Hardware Reference Signal-to-Connector Mapping

| Pod                        | 2x20<br>pin        | Analyzer<br>Bit          | APIC<br>Signal | Analyzer<br>Labels<br>Cycle 1  | Analyzer<br>Labels<br>Cycle 2                            | Analyzer<br>Labels<br>Cycle 3    |

|----------------------------|--------------------|--------------------------|----------------|--------------------------------|----------------------------------------------------------|----------------------------------|

| P2                         | 3                  | CLK1                     |                | VALID                          | VALID                                                    | VALID                            |

| P2<br>P2<br>P2<br>P2<br>P2 | 7<br>9<br>11<br>13 | D15<br>D14<br>D13<br>D12 |                | error<br>error<br>error<br>EOI | UData/Prior<br>UData/Prior<br>UData/Prior<br>UData/Prior | LData<br>LData<br>LData<br>LData |

| P2                         | 15                 | D11                      |                | C1 Stat                        | UData/Prior                                              | LData                            |

| P2                         | 17                 | D10                      |                | C1 Stat                        | UData/Prior                                              | LData                            |

| P2                         | 19                 | D9                       |                | A Stat                         | UData/Prior                                              | LData                            |

| P2                         | 21                 | D8                       |                | A Stat                         | UData/Prior                                              | LData                            |

| P2                         | 23                 | D7                       |                | A1Stat                         | UData/A2Stat                                             | LData                            |

| P2                         | 25                 | D6                       |                | A1Stat                         | UData/A2Stat                                             | LData                            |

| P2                         | 27                 | D5                       |                | DestMo                         | UData                                                    | LData                            |

| P2                         | 29                 | D4                       |                | Delive                         | UData                                                    | LData                            |

| P2                         | 31                 | D3                       |                | Delive                         | UData                                                    | LData                            |

| P2                         | 33                 | D2                       |                | Delive                         | UData                                                    | LData                            |

| P2                         | 35                 | D1                       |                | Level                          | UData                                                    | LData                            |

| P2                         | 37                 | D0                       |                | Trigge                         | UData                                                    | LData                            |

Two-Pod Logic Analyzer Signal List

E2467A APIC Bus Preprocessor Interface

| Pod                  | 2x20<br>pin          | Analyzer<br>Bit          | APIC<br>Signal | Analyzer<br>Labels<br>Cycle 1        | Analyzer<br>Labels<br>Cycle 2 |  |

|----------------------|----------------------|--------------------------|----------------|--------------------------------------|-------------------------------|--|

| P1                   | 3                    | CLK1                     |                | PICCLK                               | PICCLK                        |  |

| P1<br>P1<br>P1<br>P1 | 7<br>9<br>11<br>13   | D15<br>D14<br>D13<br>D12 |                | cycle<br>cycle<br>ArbID<br>ArbID     | cycle<br>cycle                |  |

| P1<br>P1<br>P1<br>P1 | 15<br>17<br>19<br>21 | D11<br>D10<br>D9<br>D8   |                | ArbID<br>ArbID<br>Vector<br>Vector   |                               |  |

| P1<br>P1<br>P1<br>P1 | 23<br>25<br>27<br>29 | D7<br>D6<br>D5<br>D4     |                | Vector<br>Vector<br>Vector<br>Vector |                               |  |

| P1<br>P1<br>P1<br>P1 | 31<br>33<br>35<br>37 | D3<br>D2<br>D1<br>D0     | D1<br>D0       | Vector<br>Vector<br>PICD1<br>PICD0   |                               |  |

Four-Pod Logic Analyzer Signal List

E2467A APIC Bus Preprocessor Interface

#### Preprocessor Interface Hardware Reference Signal-to-Connector Mapping

| Pod                  | 2x20<br>pin          | Analyzer<br>Bit          | APIC<br>Signal | Analyzer<br>Labels<br>Cycle 1          | Analyzer<br>Labels<br>Cycle 2 |

|----------------------|----------------------|--------------------------|----------------|----------------------------------------|-------------------------------|

| P2                   | 3                    | CLK1                     |                | VALID                                  | VALID                         |

| P2<br>P2<br>P2<br>P2 | 7<br>9<br>11<br>13   | D15<br>D14<br>D13<br>D12 |                | error<br>error<br>error<br>EOI         |                               |

| P2<br>P2<br>P2<br>P2 | 15<br>17<br>19<br>21 | D11<br>D10<br>D9<br>D8   |                | C1 Stat<br>C1 Stat<br>A Stat<br>A Stat |                               |

| P2<br>P2<br>P2<br>P2 | 23<br>25<br>27<br>29 | D7<br>D6<br>D5<br>D4     |                | A1Stat<br>A1Stat<br>DestMo<br>Delive   |                               |

| P2<br>P2<br>P2<br>P2 | 31<br>33<br>35<br>37 | D3<br>D2<br>D1<br>D0     |                | Delive<br>Delive<br>Level<br>Trigge    |                               |

Four-Pod Logic Analyzer Signal List

E2467A APIC Bus Preprocessor Interface

# Preprocessor Interface Hardware Reference Signal-to-Connector Mapping

| Pod                  | 2x20<br>pin          | Analyzer<br>Bit          | APIC<br>Signal | Analyzer<br>Labels<br>Cycle 1                    | Analyzer<br>Labels<br>Cycle 2 |

|----------------------|----------------------|--------------------------|----------------|--------------------------------------------------|-------------------------------|

| P3                   | 3                    | CLK1                     |                |                                                  |                               |

| P3<br>P3<br>P3<br>P3 | 7<br>9<br>11<br>13   | D15<br>D14<br>D13<br>D12 |                | DestID<br>DestID                                 |                               |

| P3<br>P3<br>P3<br>P3 | 15<br>17<br>19<br>21 | D11<br>D10<br>D9<br>D8   |                | DestID<br>DestID<br>DestID<br>DestID             |                               |

| P3<br>P3<br>P3<br>P3 | 23<br>25<br>27<br>29 | D7<br>D6<br>D5<br>D4     |                | DestID<br>DestID<br>S Stat/TieID<br>S Stat/TieID |                               |

| P3<br>P3<br>P3<br>P3 | 31<br>33<br>35<br>37 | D3<br>D2<br>D1<br>D0     |                | C2Stat/TieID<br>C2Stat/TieID                     |                               |

Four-Pod Logic Analyzer Signal List

E2467A APIC Bus Preprocessor Interface

#### Preprocessor Interface Hardware Reference Signal-to-Connector Mapping

| Pod                  | 2x20<br>pin          | Analyzer<br>Bit      | APIC<br>Signal | Analyzer<br>Labels<br>Cycle 1    | Analyzer<br>Labels<br>Cycle 2    |

|----------------------|----------------------|----------------------|----------------|----------------------------------|----------------------------------|

| P4                   | 3                    | CLK1                 |                |                                  |                                  |

| P4                   | 7                    | D15                  |                | UData/Prior                      | LData                            |

| P4                   | 9                    | D14                  |                | UData/Prior                      | LData                            |

| P4                   | 11                   | D13                  |                | UData/Prior                      | LData                            |

| P4                   | 13                   | D12                  |                | UData/Prior                      | LData                            |

| P4                   | 15                   | D11                  |                | UData/Prior                      | LData                            |

| P4                   | 17                   | D10                  |                | UData/Prior                      | LData                            |

| P4                   | 19                   | D9                   |                | UData/Prior                      | LData                            |

| P4                   | 21                   | D8                   |                | UData/Prior                      | LData                            |

| P4                   | 23                   | D7                   |                | UData/A2Stat                     | LData                            |

| P4                   | 25                   | D6                   |                | UData/A2Stat                     | LData                            |

| P4                   | 27                   | D5                   |                | UData                            | LData                            |

| P4                   | 29                   | D4                   |                | UData                            | LData                            |

| P4<br>P4<br>P4<br>P4 | 31<br>33<br>35<br>37 | D3<br>D2<br>D1<br>D0 | D1<br>D0       | UData<br>UData<br>UData<br>UData | LData<br>LData<br>LData<br>LData |

Four-Pod Logic Analyzer Signal List

E2467A APIC Bus Preprocessor Interface

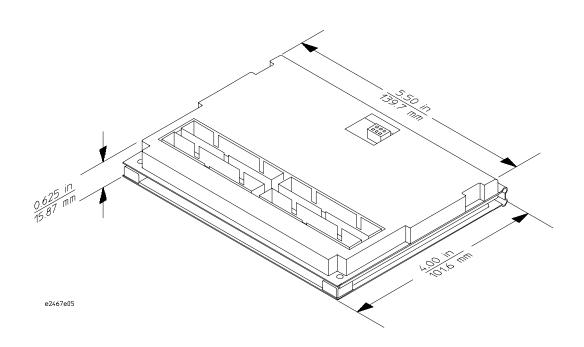

### **Circuit Board Dimensions**

The following figure gives the dimensions for the preprocessor interface assembly. The dimensions are listed in inches and millimeters.

Dimensions

E2467A APIC Bus Preprocessor Interface

### **Repair Strategy**

The repair strategy for this preprocessor interface is board replacement. However, the following table lists some mechanical parts that may be replaced if they are damaged or lost. Contact your nearest Hewlett-Packard Sales Office for further information on servicing the board.

#### **Replaceable Parts**

| HP Part Number | Description                  |

|----------------|------------------------------|

| E2467-69501    | Circuit board assembly       |